당신은 주제를 찾고 있습니까 “esd 회로 – ESD Basic“? 다음 카테고리의 웹사이트 https://hu.taphoamini.com 에서 귀하의 모든 질문에 답변해 드립니다: https://hu.taphoamini.com/photos/. 바로 아래에서 답을 찾을 수 있습니다. 작성자 백동철 이(가) 작성한 기사에는 조회수 5,361회 및 좋아요 34개 개의 좋아요가 있습니다.

Table of Contents

esd 회로 주제에 대한 동영상 보기

여기에서 이 주제에 대한 비디오를 시청하십시오. 주의 깊게 살펴보고 읽고 있는 내용에 대한 피드백을 제공하세요!

d여기에서 ESD Basic – esd 회로 주제에 대한 세부정보를 참조하세요

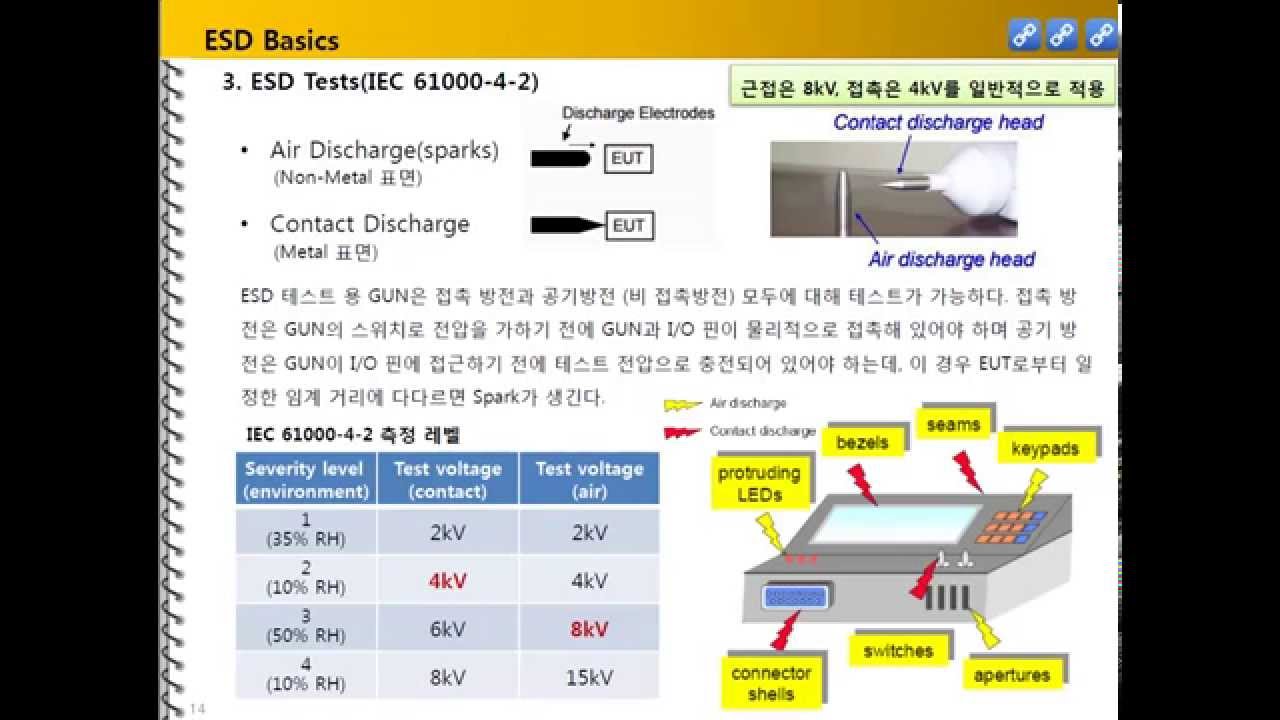

ESD EOS Basic MODEL HBM CDM MM IEC DEVICE Protection

정전기 기초 모델

esd 회로 주제에 대한 자세한 내용은 여기를 참조하세요.

ESD 보호 설계 방법 – 시간으로부터 자유하다

ESD 보호를 위한 설계는 외부와 인터페이스하는 모든 회로에 필수적이다. ESD failure은 외부 인터페이스용 커넥터가있는 곳에서 경우가 종종 발생 …

Source: tozest.tistory.com

Date Published: 8/5/2022

View: 9821

CMOS 회로 설계의 ESD 보호

ESD 보호는 입력 핀 또는 출력 핀의 ESD 보호 설계 문제일 뿐만 아니라 전체 칩의 ESD 보호 문제입니다. 각 입출력 회로 칩에서 해당 ESD 보호 회로를 …

Source: www.shunlongwei.com

Date Published: 7/12/2022

View: 5457

ESD 보호 커패시터 선택 방법 – 자주 묻는 질문

한 물체에서 다른 물체로 전자가 급속하게 이동하는 것이 ESD입니다. ESD는 전자회로 및 부품에는 적으로 여겨집니다. 전자 부품으로의 전하의 이동은 …

Source: forum.digikey.com

Date Published: 6/27/2021

View: 3831

다이오드와 제너 다이오드 회로 – 네이버 블로그

ESD Protection Diode에 대해 조사하다가, 설명이 여기가 가장 잘 되있고, 자세하게 나와서 이해하는 데 많은 도움이 된 곳이다.

Source: m.blog.naver.com

Date Published: 5/7/2022

View: 2636

ESD 보호의 필요성 및 설계 원칙 분석

ESD (정전기 방전)는 CMOS 회로의 심각한 고장 메커니즘 중 하나이며, 회로 자체가 연소 될 수 있습니다. CMOS 집적 회로에 대한 ESD 보호의 필요성에 …

Source: m.ko.gnscomponent.com

Date Published: 3/7/2021

View: 7299

고전압 소자용 esd 보호회로 및 이를 구비한 반도체 소자

본 발명은 정전방전(ESD; Electro static Discharge) 현상으로부터 집적회로의 내부소자를 보호하기 위한 ESD 보호 회로에 관한 것이다. 본 발명의 ESD 보호회로는, …

Source: patents.google.com

Date Published: 8/27/2022

View: 2725

SCR 기반 양방향성 ESD보호회로의 설계 변수 변화에 따른 …

GGNMOS 구조의. ESD 보호회로는 높은 ESD 전류를 기생적으로 생기. 는 Lateral npn BJT에 의해 효율적으로 방전시키므. 로 반도체 칩에서 정전기 문제를 해결하기 위한 ESD.

Source: www.koreascience.or.kr

Date Published: 7/15/2021

View: 6371

주제와 관련된 이미지 esd 회로

주제와 관련된 더 많은 사진을 참조하십시오 ESD Basic. 댓글에서 더 많은 관련 이미지를 보거나 필요한 경우 더 많은 관련 기사를 볼 수 있습니다.

주제에 대한 기사 평가 esd 회로

- Author: 백동철

- Views: 조회수 5,361회

- Likes: 좋아요 34개

- Date Published: 2015. 6. 17.

- Video Url link: https://www.youtube.com/watch?v=g56JwiXRcLg

ESD 보호 설계 방법

ESD 보호를 위한 설계는 외부와 인터페이스하는 모든 회로에 필수적이다.

ESD failure은 외부 인터페이스용 커넥터가있는 곳에서 경우가 종종 발생한다.

ESD 보호 요구 사항 (ESD protection specification)

반도체 부품은 정전기 방지 환경(제조공정)에서 뿐만 아니라 사용자 환경에 노출 될 수 있기 때문에 ESD 보호 설계가 필요하다.

외부 포트에 연결할 때 사용자는 대게 ESD에 대해 주의를 기울이지 않는다. 따라서 모든 외부 포트를 ESD로부터 완벽하게 보호해야 한다.

최근 전자 장치 ESD spec은 contact 8kV (즉, 금속 접촉을 통해 8kV가 핀으로 직접 방전되는 경우) 또는 Air 15kV (15kV 지점이 핀에 가깝고 공극을 통한 방전)에서 failure이 발생하지 않는 것이 목표다.

모든 전자 장치가 이 spec을 만족하는 하는 것은 아니며, 또한 외부에서 유입되는 ESD level은 이보다 클 수 있다. 따라서 회로 내부뿐만 아니라 외부에서 ESD 보호 하는 방법을 추가 해야 한다.

ESD 보호 회로 설계 방법

외부 입/출력 (I / O) 라인에 장치를 보호하기위한 ESD 회로의 핵심은, 인터페이스 장치를 손상시키는 레벨 위로 전압이 상승하는 것을 방지하는 것이다. 이것은 peak전압을 clamping하는 회로를 사용하여 달성 할 수 있다.

일반적으로 Power와 Ground rail 사이에 삽입한다.

전압 clamping에 사용할 수있는 일반적인 회로는 Dual diode이다.

다이오드는 Reverse bias가 인가될때 낮은 수준의 leakage 전류를 가져야하며, Forward bias일때는 Ron 저항이 낮아야 한다. 또한, 커패시턴스가 낮아야 고속 주파수 응답 / 데이터 속도를 만족시킬 수 있다.

보호를 위해 회로 입력에 사용되는 다이오드

다이오드 D1 및 D2가 회로 정상 동작할때는 reverse bias가 인가 되기때문에 커패시턴스성분만 보일뿐, 회로동작엔 영향을 주지 않는다. ESD event시에 입력 전압이 Power 전압 이상으로 올리는 펄스가 발생하면 상단 다이오드 D1이 작동합니다. 마찬가지로 전압이 Ground 전압 아래로 떨어지면 다른 다이오드 D2가 작동합니다. 일반 신호 다이오드를 사용하면, 입력 라인에서 예상되는 최대 전압 여행은 레일 위 + 0.5V, 접지 아래 -0.5V 정도다. 이 문턱전압은 diode 특성에 따라 가변적이다.

정전기 방전에 대한 일반적인 응답 곡선은 IEC61000-4-5에 의해 정의되며 일반적인 정전기 방전 곡선은 아래 그림과 같다. 파형의 상승 시간은 약 1ns이며 전류 레벨은 30A에서 피크입니다. 이러한 전압을 억제하려면 매우 효과적인 Clamping 회로가 필요하며 ESD 설계 spec을 정할때, 허용 가능한 구성 요소 및 성능 한계를 지정해야 한다.

ESD PCB 설계

ESD 억제를 위해 내부 보호 회로 잘 설계하는 것 외에도 인쇄 회로 기판 PCB 설계 및 레이아웃도 매우 중요하다.

PCB 설계시 ESD 억제에 대한 요구 사항을 충족시키는 데 투자하면 debugging 하는데 용을 많이 줄일 수 있고, ESD 문제가 줄어듦에 따라 최종 장비의 전반적인 안정성이 향상된다.

모든 인쇄 회로 기판 PCB 설계에서 ESD에 의한 failure를 최소화 하기 위한 몇가지 기본 설계 지침이 있다.

회로 루프 제거 : 라인의 루프(기전력 효과) 는 유도로 인해 원하지 않는 전류가 발생할 수 있습니다. 이로 인해 일반적인 원치 않는 픽업으로 인한 성능이 저하 될 수 있다. ESD 보호 하기위해 루프가 존재하지 않도록 주의해야 한다.

라인의 루프(기전력 효과) 는 유도로 인해 원하지 않는 전류가 발생할 수 있습니다. 이로 인해 일반적인 원치 않는 픽업으로 인한 성능이 저하 될 수 있다. ESD 보호 하기위해 루프가 존재하지 않도록 주의해야 한다. 인쇄 회로 기판의 접지(ground) plane layer 사용 : 접지 루프를 줄이는 한 가지 방법은 인쇄 회로 기판 내에 접지면을 사용하는 것입니다. 이를 통해 모든 신호를 효과적으로 접지하고 접지 루프의 가능성을 줄일 수 있다.

접지 루프를 줄이는 한 가지 방법은 인쇄 회로 기판 내에 접지면을 사용하는 것입니다. 이를 통해 모든 신호를 효과적으로 접지하고 접지 루프의 가능성을 줄일 수 있다. 라인 길이를 줄이십시오 : 모든 와이어는 안테나 역할을합니다. ESD 펄스에 의해 나타나는 매우 짧은 상승 시간으로 모든 안테나는 고전압 스파이크를 수신 할 수 있습니다. 선로 길이를 줄이면 수신되는 복사 에너지 수준이 줄어들고 정전기 방전으로 인한 스파이크가 줄어 든다.

모든 와이어는 안테나 역할을합니다. ESD 펄스에 의해 나타나는 매우 짧은 상승 시간으로 모든 안테나는 고전압 스파이크를 수신 할 수 있습니다. 선로 길이를 줄이면 수신되는 복사 에너지 수준이 줄어들고 정전기 방전으로 인한 스파이크가 줄어 든다. 보호 회로 주변의 기생 인덕턴스 감소 : 많은 전자 회로에는 ESD 보호 회로가 삽입돼 있는데, 이는 기생 인덕턴스 수준이 낮은 경우에만 효과적입니다. PCB 설계에서 발생하는 기생 인덕턴스는이 영역의 라인 길이를 특히 짧게 유지하고 트랙 폭을 늘림으로써 줄일 수 있다.

많은 전자 회로에는 ESD 보호 회로가 삽입돼 있는데, 이는 기생 인덕턴스 수준이 낮은 경우에만 효과적입니다. PCB 설계에서 발생하는 기생 인덕턴스는이 영역의 라인 길이를 특히 짧게 유지하고 트랙 폭을 늘림으로써 줄일 수 있다. PCB edge에 소자를 배치하지 말자. 뾰족한 부분은 Electro staic이 잘 방전하는 부분이므로, 가능하면 입력 및 출력 라인이나, 소자를 배치하지 않는 것이 좋다.

외부 연결이 가능한 모든 품목에는 ESD의 영향으로부터 보호해야 한다. 위에 설명한 방식으로 장치를 보호함으로써 공개 시장에서 판매하기 위해 필요할 수있는 인증을 받을 수 있다. ESD immunity를 확보하기 위해서는 설계 초기 단계에서 ESD spec을 고려해 공간을 할당해야한다. 설계 후반에 필요한 수정은 구현하기 어렵고 비용이 많이 든다.

파트너스 활동을 통해 일정액의 수수료를 제공받을 수 있음

[실무] ESD 및 서지 보호 회로 설계하기 (ft. TVS)

반응형

TVS를 활용한 ESD 보호회로 예시 (by Altium)

1. ESD 란?

ESD는 쉽게 말해서 정전기이다. 회로가 동작할 때 전하가 축적되어 스스로 발생할 수도 있고 사람 손에 의해서 발생할 수도 있다. ESD는 순간적이지만 IC 소자를 태워버릴 수 있다.

따라서, 전자회로를 설계하는 엔지니어라면, 심지어 반도체를 설계하는 연구원도 꼭 설계해야하는 것이 바로 ESD 보호회로와 서지 보호회로이다. 보통 반도체 레벨에선 ESD 보호회로까진 들어간다. 그렇지만 반도체라는 것이 워낙 작다보니 전기적 용량이 크지 않기 때문에 ESD 보호회로를 IC 외부에 추가적으로 구성해야 한다. 또한 ESD를 보호하는 목적으로 설계를 하다 보면 서지도 보호가 되는 효과가 있다.

ESD 모델 for CDM, HBM and IEC (by Ti)

참고로 EMC 테스트에서 ESD항목이 있는데, 이 때는 IEC 스탠다드를 따른다(IEC61000 혹은 KN61000 참조).

2. ESD 보호회로

2-1. ESD 보호회로의 역할

ESD 보호회로의 역할과 효과를 아주 심플하게 아래의 그림으로 이해할 수 있다.

ESD 보호회로 효과 및 전압 파형 (by TI)

다이오드의 Vf를 넘는 순간 다이오드를 통해 전류가 그라운드로 빠져나간다. 그래서 IC로 전류가 흐르지 않아 보호가 되는 원리이다. 재밌는 것은 아래의 그래프이다. ESD Diode가 없는 경우엔 300V에 달하는 전압이 IC를 강타하는데, 그러고 음전압 -100V까지 내려가 전기적 충격이 양방향에서 가해진다는 것이다.

2-2. ESD 보호회로 설계하기 (도면 SCM)

가장 심플한 것은 TVS를 활용하는 것이다. TVS는 양방향으로 된 다이오드라고 생각하면 된다. 따라서 음전압과 양전압 모두 클램핑 해준다.

+- 양방향 클램핑이 중요한 이유는 위에 ESD 전압 파형을 보면 쉽게 이해할 수 있다.

TVS를 활용한 ESD 보호회로 예시 (by Altium)

위 예시는 전형적인 ESD 보호회로이다. TVS를 활용하였다.

Zenor Diode를 활용한 버퍼 IO ESD 보호회로 (by Altium)

버퍼에 다이오드를 활용하여 ESD 보호회로를 설계할 수도 있다. (대개 Buffer를 사용하는 이유 또한 보호목적 이다.)

이런 ESD 회로는 반도체 칩이나 전자회로나 똑같이 적용되는 부분이다.

2-3. ESD 보호회로 설계하기 (PCB Artwork)

TVS 다이오드 아트웍 (By Altium)

커넥터(ESD 소스) 근처에 TVS를 배치한다. IC까지의 경로상에 TVS가 있어야 한다.

↓↓실무 고급 기술★↓↓

기생 인덕턴스 줄이기: 패턴 길이 짧게

기생 인덕턴스 줄이기: 다층 전원 플레인

Current Loop 제거

설명:

PCB 패턴에 의해 기생 인덕턴스가 생겨서 TVS 다이오드의 클램핑 전압이 원하는 값 이상으로 상승할 수 있습니다. 따라서 패턴 길이를 줄이고 별도의 접지 및 전원 플레인을 가진 다층 PCB를 설계하여 기생 인덕턴스를 최소화하는 것이 중요합니다. 이외에도 TVS 다이오드의 폼 팩터가 작으면 기생 인덕턴스를 낮출 수 있습니다.

그리고 Current Loop를 제거하는 것도 중요합니다. Loop에서 current spike가 유도될 수 있거든요.

3. References

이상 초보자부터 실무자 레벨까지의 ESD Protection에 대해 알아봤습니다.

제 글을 참조하여 완성도 높은 설계가 되었으면 합니다.

도움이 되었다면 즐겨찾기 추가, 공감 및 댓글 부탁드려요!

반응형

ESD(반도체 정전기 대책, ESD 모델 이유)

반응형

1. ESD란 ( 정전기 : Electrostatic Discharge)

다른 전위를 갖는 두 물체 사이에서 발생하는 마찰에 의한 전하 이동입니다.

나노 세컨드의 매우 짧은 시간에 어떤 상황에서든 발생할 수 있는 현상입니다.

오늘날에는 IC 고집적화로 인해 약간은 정전기 만으로 회로에 손상을 줄 수 있으며, 한 번에 더 많은 반도체에 데미지를 줄 수 있으므로 ESD를 방지하는 것은 생산성과 제품의 신뢰성에 영향을 미치는 중요한 요인이 되었습니다.

따라서 칩 내부에 ESD 보호 회로를 내장하여 ESD 발생 시 내부 회로로의 유입을 방지하고 외부로 ESD를 방전시킬 수 있어야 합니다.

2. ESD 발생 모델

ESD 발생에는 세가지 모델이 있습니다.

첫 번째 HBM : Human Body Model

두 번째 MM : Machine Model

세 번째 CDM : Charge Device Modle

1) HBM(Human Body Model)

대부분의 ESD가 일어나는 모델로 사람에 의해 발생한 정전기가 문제가 됩니다.

여러가지 마찰에 의해 인체에 축적된 불안전한 전하가 사람 손끝을 통해 IC 핀 등을 만짐으로 IC 속으로 방전되어 회로를 파괴시키는 현상입니다.

인체 내부에는 커패시터가 존재하고 마찰에 의한 전하가 축적 되어있습니다. 이 때 IC 칩과 마찰이 일어나면 수 KV의 전압이 걸려 다이오드가 파괴되고 높은 전류 때문에 IC 칩이 파괴됩니다.

인체의 커패시턴스는 100에서 200피코 패럿 정도이고 저항은 100~200옴, 손끝 피부접촉저항은 1k~수십k옴이라고 합니다. 이러한 조건으로 겨울철 의자에서 손으로 부품을 조립하는 경우 인체에 대전되는 전력을 구해보면 3.6mJ정도로 IC 파괴 에너지보다 훨씬 크기 때문에 IC 칩을 망가뜨리기 충분합니다.

2) CDM(Charged Device Model 정전 모형 )

인체모형과는 정 반대의 개념으로 방전에 의한 회로 파괴 현상입니다.

부품의 운반, 보관, 취급 등의 과정에서 도체 물질과 대전이 이루어지면 IC 내부의 전하가 바깥으로 급속하게 방전되어 발생합니다.

3) MM(Machine Model 기계모형 )

반도체 제조 공정 중에 장비나 기타 금속에 마찰하면서 이뤄지는 ESD 현상입니다.

3. ESD 보호 회로

이렇게 다양한 ESD에 의한 불량을 막기 위해서는 IC 칩엔 ESD 보호 회로가 꼭 동반되어야 합니다.

ESD 보호 회로는 모든 입출력핀에 존재하고, 이 ESD 보호 회로에 의해 ESD 때문에 발생하는 전류는 입출력핀에서 내부 회로로 들어가지 않고 그라운드로 빠져버립니다.

이때 ESD 보호 회로 사이에 저항을 연결해 주는데, 저항은 ESD에 의해 발생하는 전류가 너무 클 경우 ESD 보호 회로 또한 망가질 수 있기 때문에 ESD 전류를 제한하기 위해 넣어준 것입니다.

1) 다이오드를 사용한 보호 회로

ESD 보호 회로중 가장 기본적인 다이오드를 이용한 보호 회로입니다.

다이오드를 이용한 보호 회로는 두 개의 다이오드와 두 개의 저항으로 이뤄집니다.

두 개의 저항인 R1과 R2는 다이오드 D1과 D2가 도통될 때 과도한 전류가 흐르지 않게 억제하는 역할을 하면서 ESD 펄스가 내부회로에 전달되기 전 RC 딜레이를 줘서 ESD 전류가 다이오드로 빠져나갈 수 있도록 해주는 역할을 합니다.

상황 1) 양의 ESD 전압이 가해졌을 때 D1을 통해 Vdd로 ESD 전압이 빠져나가게 됩니다.

상황 2) 음의 ESD 전압이 가해졌을 때 D2를 통해 Vss로 ESD 전압이 빠져나가게 됩니다.

이로서 회로를 ESD로부터 보호할 수 있습니다.

2) GGNMOS(Gate Ground NMOS)

Gate, Source, Substrate를 GND에 연결하고 Darin은 IO Pad와 연결한 보호 회로입니다.

ESD에 의해 Drain에 강한 전계가 걸리면 이 전계에 의해 P 기판에는 정공이 모이게 됩니다.

이러한 현상은 베이스에 순방향 전압이 걸리는 것과 같습니다.

그렇기 때문에 베이스와 컬렉터에는 역방향 전압이 걸리게 되고, 베이스와 에미터에는 순방향 전압이 걸리는 것이므로 NPN BJT가 동작하는 것 처럼 됩니다.

이 때 ESD 전류는 내부 회로로 가지 않고 쇼트된 게이트 GND nMOS를 통해 나가게 됩니다.

이 때문에 생기는 장점이 있는데 Gate GND Nmos는 MOSFET을 이용하는 것이기에 설계가 용이하고 CMOS 공정과 높은 호환성을 가지는 장점이 있습니다.

그런 아쉽게도 GGNMOS는 보호회로가 다소 많은 공간을 차지하는 단점이 있습니다.

3) SCR(Silicon Controlled Rectifier)

PN 접합 2개가 이어진 구조입니다.

SCR의 매커니즘을 알아보도록 하겠습니다.

먼저 SCR에 순방향전압을 인가합니다. 그러면 N1과 P2사이의 공간전하 영역(S2)이 넓어지면서 전류가 흐르지 않는 상태가 됩니다.

게이트 전압에 의해 N2로부터 전자들이 추가로 P2로 이동해 P2 지역은 전자가 과잉됩니다.

P2 지역에 과잉된 전자들에 의해 공간전하영역 S2가 소멸하게 됩니다.

이미 SCR에는 순방향 전압을 걸어놓았기에 전자는 S1을 거쳐 에노드 전극에 도달합니다.

역으로 에노드 전극으로부터 많은 정공이 캐소드로 이동하게되고, 이동하는 정공수가 증가함에 따라 이동하는 전자 수도 증가하게 됩니다.

이렇게 전자와 정공의 이동이 많게 되면 N1은 P형 반도체로 P2는 N형 반도체로 바뀌게 됩니다.

N1과 P2가 바뀌게 되면 단순한 PN 접합과 같이 변했기 때문에 게이트전압에 상관없이 역방향전압이 되어도 계속 도통상태가 됩니다.

이후 ESD가 모두 빠져나가 통과전류가 0이 되면 도통을 멈추고 원래 PNPN형태로 돌아가게 됩니다.

SCR은 좋은 스위칭 특성, 높은 전류 구동 능력, 저면적 저전력 회로에 ESD 보호 소자로 적용 가능합니다.

그러나 높은 트리거 전압과 낮은 홀딩 전압으로 ESD 설계영역을 최적화하기 힘들다는 단점이 존재합니다.

반응형

Engineering and Component Solution Forum – TechForum │ Digi-Key

We use cookies to provide our visitors with an optimal site experience. View our privacy notice and cookie notice to learn more about how we use cookies and how to manage your settings. By proceeding on our website you consent to the use of cookies.

다이오드와 제너 다이오드 회로

i-매거진

초보자나 신입사원의 경우, 학교에서 회로에 대해 많이 배웠다고 생각하지만 막상 실무에서는 어떤 회로를 사용해야 할지 가늠도 할 수 없을 때가 많다. 이와 관련, 본지에서는 관련 분야의 전문가들이 실제로 사용하는 회로와 상수를 구하는 방법, 그리고 경험에서 얻어진 노하우에 대해 상세히 소개한다. 다이오드와 제너 다이오드의 응용 다이오드 응용 회로 다이오드는 정류 작용을 갖고 있는 유용한 반도체 소자이며 다방면에 사용되고 있다. 여기서는 그 정류 작용을 활용한 보호 회로와 정류/검파/절대값 회로에 대해 소개하도록 한다. 다이

magazine.hellot.net

KR20060078152A – 고전압 소자용 esd 보호회로 및 이를 구비한 반도체 소자 – Google Patents

H — ELECTRICITY

H01 — BASIC ELECTRIC ELEMENTS

H01L — SEMICONDUCTOR DEVICES; ELECTRIC SOLID STATE DEVICES NOT OTHERWISE PROVIDED FOR

H01L27/00 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

H01L27/02 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

H01L27/04 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

H01L27/08 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

H01L27/085 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

H01L27/088 — Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

키워드에 대한 정보 esd 회로

다음은 Bing에서 esd 회로 주제에 대한 검색 결과입니다. 필요한 경우 더 읽을 수 있습니다.

이 기사는 인터넷의 다양한 출처에서 편집되었습니다. 이 기사가 유용했기를 바랍니다. 이 기사가 유용하다고 생각되면 공유하십시오. 매우 감사합니다!

사람들이 주제에 대해 자주 검색하는 키워드 ESD Basic

- ESD EOS Basic MODEL HBM CDM MM IEC DEVICE Protection

ESD #Basic

YouTube에서 esd 회로 주제의 다른 동영상 보기

주제에 대한 기사를 시청해 주셔서 감사합니다 ESD Basic | esd 회로, 이 기사가 유용하다고 생각되면 공유하십시오, 매우 감사합니다.